[閒聊] RTX 4090 12VHPWR熔毀原因簡單分析

看板PC_Shopping (個人電腦購買)作者parislove3 (艾草糖)時間3年前 (2022/11/06 11:51)推噓58(62推 4噓 68→)留言134則, 65人參與討論串1/2 (看更多)

以下轉自噗浪,作者是業界人士

分析得滿清楚,也有提到原生線並非完全安全

這邊摘錄重點,全部內容可看下面連結

https://www.plurk.com/p/p1lyp7

https://www.plurk.com/p/p1qnob

----------2022/10/31 09:34----------

RTX 4090 12VHPWR熔毀原因簡單分析

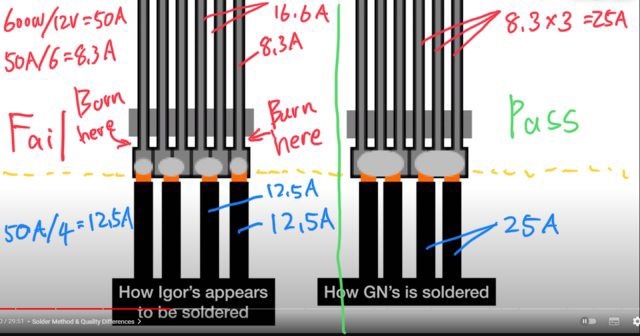

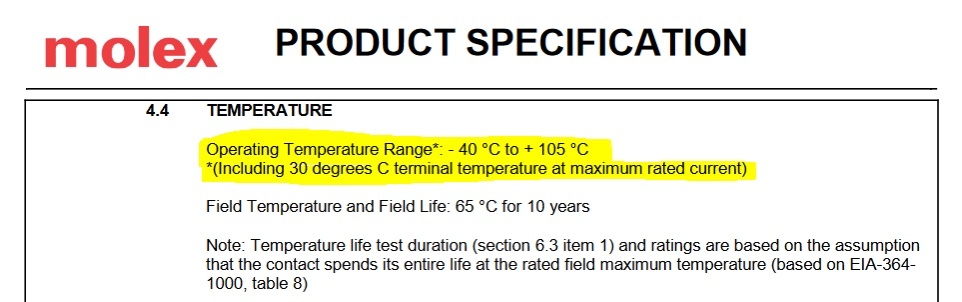

雖然是走端子承受電流規格上限

但規格以及耐溫和配PIN是沒問題的

https://images.plurk.com/5mGEELEY8FGItIBLRE7OEK.jpg

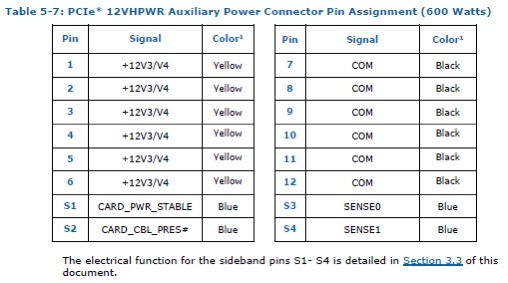

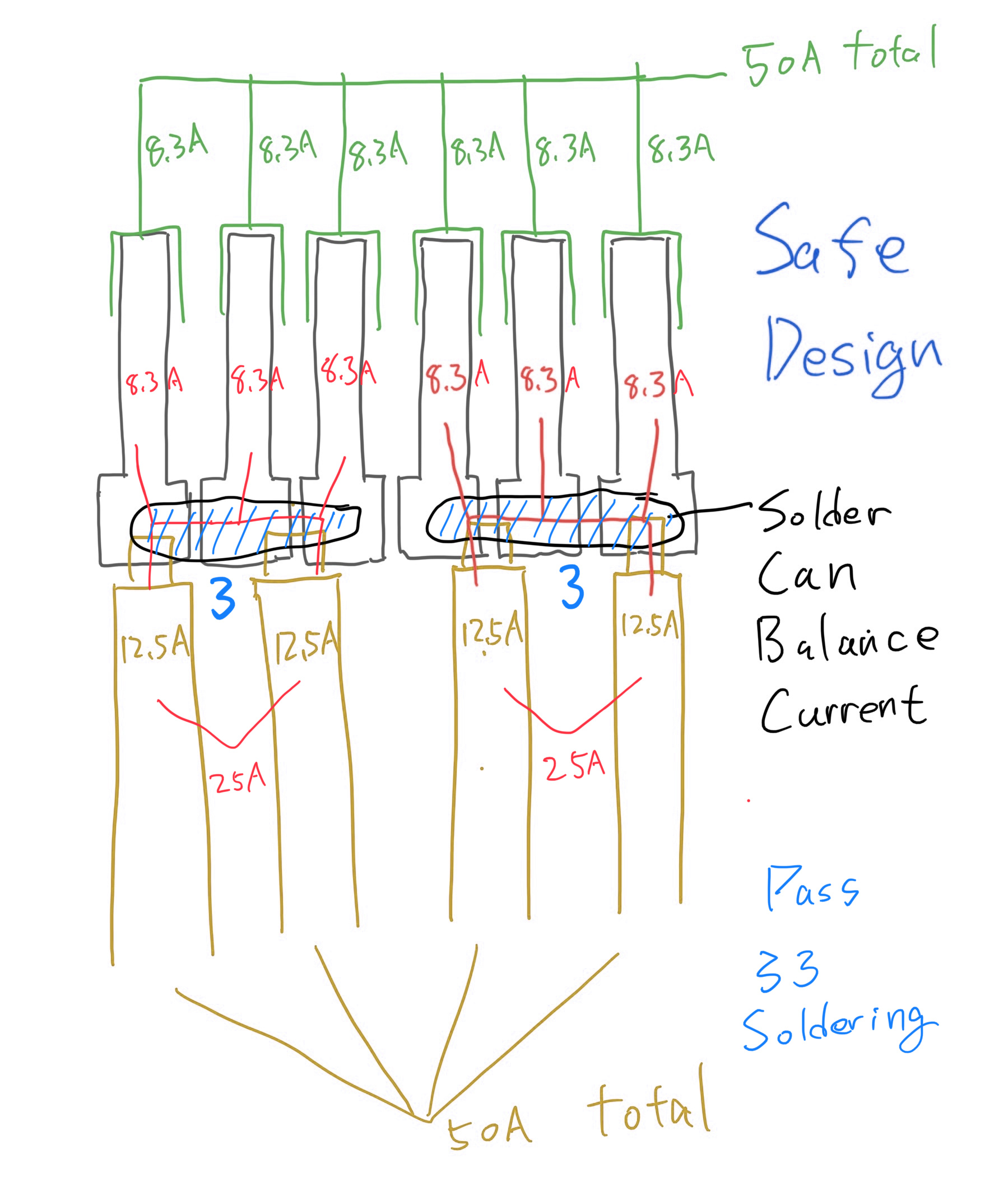

是Nvidia認證的12VHPWR一分三&一分四轉接線製作問題

電流沒有平衡所以導致都是燒靠邊邊的PIN

左邊是燒毀的線的焊接法

右邊是安全的線的焊接法

https://images.plurk.com/1qA7Oo7CTe4gQiMqAp5o1v.jpg

----------2022/10/31 09:42----------

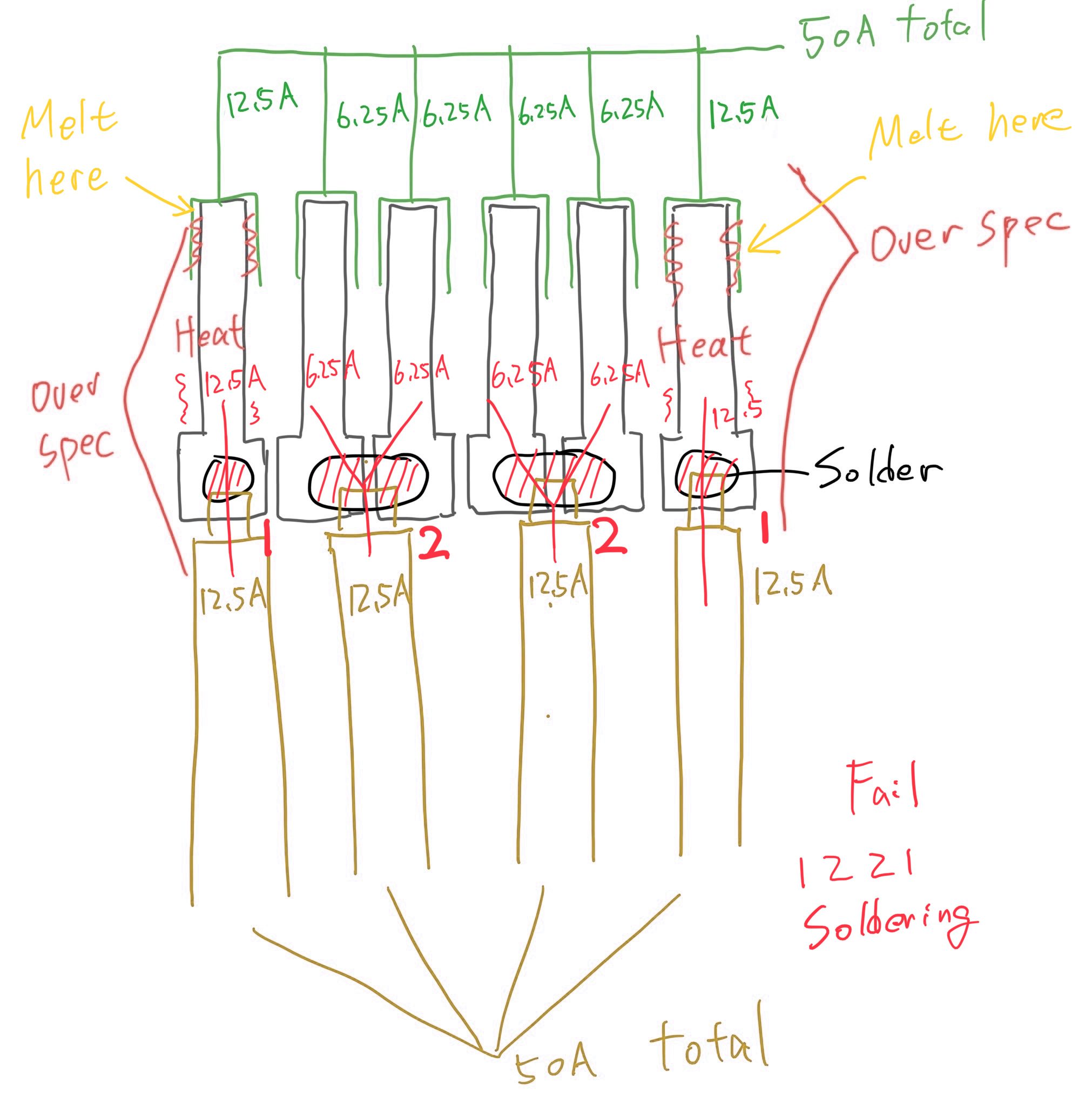

燒毀的都是因為一二二一焊接法

靠邊邊的PIN 只有8.3A耐電流

卻要承受其中一組一分四PCIE的12.5A

所以發熱就變得嚴重,不需要長時間

只要短時間高功率抽電流

幾分鐘接點就可以溫升到塑膠軟化點溫度

(因為插針熱函小溫升超快)

https://images.plurk.com/7uvtHsxcF23ks9QKYQGFeb.jpg

----------2022/10/31 09:46----------

而安全下莊的三三焊接法呢

PCIE側的兩組 12.5x2=25A可以先靠焊點匯流

再將電流均分到12VHPWR 三根PIN 上

25/3=8.3A,所以不會出現單根PIN 超過承受電流上限問題

https://images.plurk.com/Sj7A3IqkYhXOT5suEd9ug.jpg

----------2022/10/31 09:53----------

12VHWR PIN針規格是一PIN 可以連續 9A左右

----------2022/10/31 09:57----------

有人會說6PIN 全部焊一起更好啊幹嘛分3 3

因為要14AWG 四根線要焊在6個12VHPWR插針上

銲錫量會太多,反而導致焊接良率下降

所以3/3焊法是為了產線好做的折衷方案

----------2022/10/31 10:04----------

至於原生12VHPWR 接線(兩端都是12VHPWR接頭的)

如果在插針端沒有並聯起來做電流平衡

久了也是會出現類似的狀況的

不是用了原生12VHPWR線材就可以高枕無憂

只是症狀相對12VHPWR to PCIE 轉接線會比較輕微而已

----------2022/10/31 10:12----------

規格拉到太極限了

12VHPWR的插針鈑金件截面積耐電流大約才 11A

現在用到8.3A已經是 8.3/11 x100%=75%

安全餘裕剩下25%

----------2022/10/31 10:14----------

以前PCIE 8PIN 是150W,一PIN要4.2A但插針可耐8A

4.2/8 x 100%=52.5%所以還有 47.5%的餘裕

----------2022/10/31 10:24----------

三個PCIE 8一根PIN 只要流 5A左右

5 / 8 x100% = 62.5%

安全餘裕尚有37.5%

比12VHPWR的 25%安全餘裕高多了

----------2022/10/31 11:53----------

3分鐘塑膠殼外就可以從室溫25度升到50度

殼內熱源最少再加20度 = 70度

假設殼外都量到80度,殼內金屬PIN溫度就快破百囉

----------2022/10/31 15:14----------

總之銅的熔點1000度

所以只要持續供電插座針和彈片接點就會持續加熱

規格是6 mohm ( 0.006 ohm)

12.5A ^2 x 0.006 = 0.9375W

0.9W熱量加在一根牙籤粗細的銅線上

溫升要超過塑膠承受上限105度太簡單

然後因為不可能超過1000度(因為不是正負短路熔毀

所以就周邊的相鄰PIN也越來越熱然後然後就越融越多PIN

https://images.plurk.com/1ek5Y5Jb2sD6Fy3EP52HJL.jpg

https://tinyurl.com/ybnkybrx

----------2022/10/31 15:32----------

12VHPWR一根彈片和針腳面積約 0.24 cm^2

約是102℃/W ( 温升系数)

=========================

12VHPWR Over spec 一根針腳走12.5A時針腳溫升

12.5^2 x 0.006 x 102 + 25環溫= 120.6度 (遠超105度安全溫度

=========================

12VHPWR IN spec 一根針腳走8.3A時針腳溫升

8.3^2 x .006 x 102 + 25環溫= 67度 (在105度安全溫度內

----------2022/10/31 15:41----------

而且沒插好的狀況,接觸阻抗會高於規格書定義的0.006 ohm

所以實際發熱量只會更大不會更小

所以用久老化或是掰到線材

溫度只會比上面算出來的更燙,不會更低

----------2022/10/31 18:56----------

Pitch 從PCIE 的 4.2mm縮到12VHPWR的 3mm

單PIN耐受電流從PCIE 5A上升到12VHPWR 9A

大家也覺得不錯省空間30 FE也沒啥災情所以願意跟進

至於有沒有省到錢,望向這段時間零件漲價幅度

還真不知道有沒有省到錢XD

----------2022/10/31 23:39----------

我是覺得12VHPWR這Connector Set 太過實驗室了

都忘記實際投放給使用者會有多少光怪陸離的事發生

----------2022/11/04 21:40----------

12VHPWR給RTX3090 單卡約360W用

360W/12V=30A

30A/6pin = 每PIN 5A很安全

5/11 x 100%= 45% (還有55%安全餘裕

同時3090滿載使用12VHPWR發熱也只會有

5^2 x0.006 x102 +25度環溫 = 40.3度而已

----------2022/11/04 22:02----------

最怕的是公母端子不同廠商,因為製造公差關係

配對時的接觸阻抗Over Spec

----------2022/11/04 22:43----------

殼外量101度,殼內要加20度= 121度

跟我計算的失效溫升 120.6度很接近

12VHPWR Over spec 一根針腳走12.5A時針腳溫升

12.5^2 x 0.006 x 102 + 25環溫= 120.6度 (遠超105度安全溫度

https://images.plurk.com/6Jlq04FM6QBotTSXIlgNTd.jpg

--

※ 發信站: 批踢踢實業坊(ptt.cc), 來自: 218.164.86.35 (臺灣)

※ 文章網址: https://www.ptt.cc/bbs/PC_Shopping/M.1667706709.A.D3B.html

推

11/06 11:55,

3年前

, 1F

11/06 11:55, 1F

推

11/06 11:55,

3年前

, 2F

11/06 11:55, 2F

→

11/06 11:56,

3年前

, 3F

11/06 11:56, 3F

→

11/06 11:59,

3年前

, 4F

11/06 11:59, 4F

→

11/06 12:03,

3年前

, 5F

11/06 12:03, 5F

→

11/06 12:03,

3年前

, 6F

11/06 12:03, 6F

推

11/06 12:03,

3年前

, 7F

11/06 12:03, 7F

推

11/06 12:04,

3年前

, 8F

11/06 12:04, 8F

推

11/06 12:05,

3年前

, 9F

11/06 12:05, 9F

→

11/06 12:05,

3年前

, 10F

11/06 12:05, 10F

推

11/06 12:05,

3年前

, 11F

11/06 12:05, 11F

推

11/06 12:08,

3年前

, 12F

11/06 12:08, 12F

→

11/06 12:08,

3年前

, 13F

11/06 12:08, 13F

推

11/06 12:09,

3年前

, 14F

11/06 12:09, 14F

→

11/06 12:09,

3年前

, 15F

11/06 12:09, 15F

推

11/06 12:10,

3年前

, 16F

11/06 12:10, 16F

→

11/06 12:10,

3年前

, 17F

11/06 12:10, 17F

→

11/06 12:10,

3年前

, 18F

11/06 12:10, 18F

噓

11/06 12:11,

3年前

, 19F

11/06 12:11, 19F

→

11/06 12:11,

3年前

, 20F

11/06 12:11, 20F

推

11/06 12:11,

3年前

, 21F

11/06 12:11, 21F

→

11/06 12:12,

3年前

, 22F

11/06 12:12, 22F

推

11/06 12:17,

3年前

, 23F

11/06 12:17, 23F

推

11/06 12:17,

3年前

, 24F

11/06 12:17, 24F

→

11/06 12:17,

3年前

, 25F

11/06 12:17, 25F

推

11/06 12:18,

3年前

, 26F

11/06 12:18, 26F

→

11/06 12:19,

3年前

, 27F

11/06 12:19, 27F

推

11/06 12:20,

3年前

, 28F

11/06 12:20, 28F

推

11/06 12:21,

3年前

, 29F

11/06 12:21, 29F

推

11/06 12:23,

3年前

, 30F

11/06 12:23, 30F

→

11/06 12:25,

3年前

, 31F

11/06 12:25, 31F

→

11/06 12:26,

3年前

, 32F

11/06 12:26, 32F

推

11/06 12:29,

3年前

, 33F

11/06 12:29, 33F

→

11/06 12:31,

3年前

, 34F

11/06 12:31, 34F

推

11/06 12:31,

3年前

, 35F

11/06 12:31, 35F

→

11/06 12:31,

3年前

, 36F

11/06 12:31, 36F

推

11/06 12:33,

3年前

, 37F

11/06 12:33, 37F

推

11/06 12:34,

3年前

, 38F

11/06 12:34, 38F

推

11/06 12:38,

3年前

, 39F

11/06 12:38, 39F

還有 55 則推文

→

11/06 15:18,

3年前

, 95F

11/06 15:18, 95F

推

11/06 15:32,

3年前

, 96F

11/06 15:32, 96F

→

11/06 15:34,

3年前

, 97F

11/06 15:34, 97F

推

11/06 15:45,

3年前

, 98F

11/06 15:45, 98F

→

11/06 15:46,

3年前

, 99F

11/06 15:46, 99F

推

11/06 16:03,

3年前

, 100F

11/06 16:03, 100F

→

11/06 16:03,

3年前

, 101F

11/06 16:03, 101F

推

11/06 16:14,

3年前

, 102F

11/06 16:14, 102F

推

11/06 16:18,

3年前

, 103F

11/06 16:18, 103F

推

11/06 16:19,

3年前

, 104F

11/06 16:19, 104F

→

11/06 16:21,

3年前

, 105F

11/06 16:21, 105F

推

11/06 16:59,

3年前

, 106F

11/06 16:59, 106F

→

11/06 16:59,

3年前

, 107F

11/06 16:59, 107F

→

11/06 16:59,

3年前

, 108F

11/06 16:59, 108F

推

11/06 17:45,

3年前

, 109F

11/06 17:45, 109F

推

11/06 18:19,

3年前

, 110F

11/06 18:19, 110F

推

11/06 19:09,

3年前

, 111F

11/06 19:09, 111F

→

11/06 19:09,

3年前

, 112F

11/06 19:09, 112F

→

11/06 19:09,

3年前

, 113F

11/06 19:09, 113F

→

11/06 19:09,

3年前

, 114F

11/06 19:09, 114F

→

11/06 19:48,

3年前

, 115F

11/06 19:48, 115F

推

11/06 20:46,

3年前

, 116F

11/06 20:46, 116F

推

11/06 20:52,

3年前

, 117F

11/06 20:52, 117F

推

11/06 21:04,

3年前

, 118F

11/06 21:04, 118F

→

11/06 21:04,

3年前

, 119F

11/06 21:04, 119F

推

11/06 22:21,

3年前

, 120F

11/06 22:21, 120F

→

11/06 22:22,

3年前

, 121F

11/06 22:22, 121F

推

11/07 04:43,

3年前

, 122F

11/07 04:43, 122F

推

11/07 09:19,

3年前

, 123F

11/07 09:19, 123F

推

11/07 09:51,

3年前

, 124F

11/07 09:51, 124F

→

11/07 09:52,

3年前

, 125F

11/07 09:52, 125F

→

11/07 09:52,

3年前

, 126F

11/07 09:52, 126F

→

11/07 09:53,

3年前

, 127F

11/07 09:53, 127F

推

11/07 10:59,

3年前

, 128F

11/07 10:59, 128F

→

11/07 10:59,

3年前

, 129F

11/07 10:59, 129F

→

11/07 10:59,

3年前

, 130F

11/07 10:59, 130F

→

11/07 11:37,

3年前

, 131F

11/07 11:37, 131F

→

11/07 11:39,

3年前

, 132F

11/07 11:39, 132F

→

11/07 11:39,

3年前

, 133F

11/07 11:39, 133F

→

11/07 16:20,

3年前

, 134F

11/07 16:20, 134F

討論串 (同標題文章)

完整討論串 (本文為第 1 之 2 篇):

PC_Shopping 近期熱門文章

PTT數位生活區 即時熱門文章