[問題] 請教VHDL裡always的問題

程式碼:

module TEST( y, reset, clk );

output y;

input reset, clk;

reg c;

assign y = c;

always @( reset or clk )

begin

if( reset )

c = 4'b0;

else if( clk )

c = 4'b1;

end

endmodule

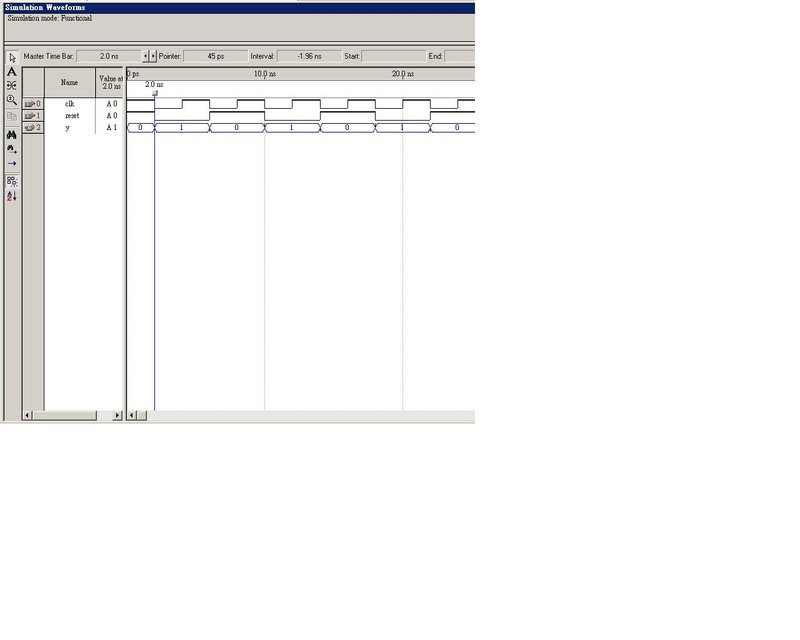

而跑出來的結果:http://images.plurk.com/1e341f7e72261158f38e7d4e9af0d46f.jpg

我的問題是: 在2ns的地方,clk為0 且 reset為0,照理說y的值應該不會變呀?!?!

可是結果卻是y變1

請高手幫忙解答,謝謝。

--

※ 發信站: 批踢踢實業坊(ptt.cc)

◆ From: 140.138.224.111

※ 編輯: rocmewtwo 來自: 140.138.224.111 (04/15 18:51)

※ 編輯: rocmewtwo 來自: 140.138.224.111 (04/15 18:53)

推

04/15 19:16, , 1F

04/15 19:16, 1F

推

04/15 19:26, , 2F

04/15 19:26, 2F

→

04/15 19:26, , 3F

04/15 19:26, 3F

→

04/15 21:35, , 4F

04/15 21:35, 4F

→

04/15 21:35, , 5F

04/15 21:35, 5F

→

04/15 21:36, , 6F

04/15 21:36, 6F

→

04/15 21:37, , 7F

04/15 21:37, 7F

→

04/15 21:37, , 8F

04/15 21:37, 8F

→

04/16 01:18, , 9F

04/16 01:18, 9F

→

04/16 01:18, , 10F

04/16 01:18, 10F

※ 編輯: rocmewtwo 來自: 140.138.224.111 (04/16 01:19)

→

04/16 01:20, , 11F

04/16 01:20, 11F

→

04/16 01:20, , 12F

04/16 01:20, 12F

→

04/16 01:21, , 13F

04/16 01:21, 13F

→

04/16 01:22, , 14F

04/16 01:22, 14F

→

04/16 01:23, , 15F

04/16 01:23, 15F

→

04/17 02:14, , 16F

04/17 02:14, 16F

→

04/17 02:15, , 17F

04/17 02:15, 17F

→

04/17 11:09, , 18F

04/17 11:09, 18F

→

04/17 13:00, , 19F

04/17 13:00, 19F

→

04/17 13:06, , 20F

04/17 13:06, 20F

→

04/17 13:07, , 21F

04/17 13:07, 21F

→

04/17 19:39, , 22F

04/17 19:39, 22F

→

04/17 19:40, , 23F

04/17 19:40, 23F

→

04/17 19:49, , 24F

04/17 19:49, 24F

→

04/17 19:50, , 25F

04/17 19:50, 25F

→

04/17 19:50, , 26F

04/17 19:50, 26F

→

04/17 20:49, , 27F

04/17 20:49, 27F

→

04/17 20:49, , 28F

04/17 20:49, 28F

→

04/17 20:49, , 29F

04/17 20:49, 29F

Programming 近期熱門文章

PTT數位生活區 即時熱門文章